Defect Analysis and Preventive Measures of QFN Device Assembly Process

QFN Package Characteristics

QFN (Quad Flat No-Lead) devices adopt a Micro Lead Frame (MLF) copper substrate packaging structure. The lead frame is directly exposed at the package bottom to serve as solder terminals, making QFN a leadless package type. The device outline is usually square or rectangular, with a large exposed thermal pad at the center of the bottom, surrounded by a matrix of smaller pads. These small pads provide electrical connections for the bare die inside. Through the reflow soldering process, QFN packages can be reliably mounted onto PCB pads.

Inside the QFN package, the bare die is wire-bonded to the pads, resulting in very low inductance and impedance, which provides excellent electrical performance for high-speed and microwave applications. During assembly, the large central exposed thermal pad is soldered directly to the thermal pad on the PCB, offering low thermal resistance, excellent heat dissipation, and very low ground resistance.

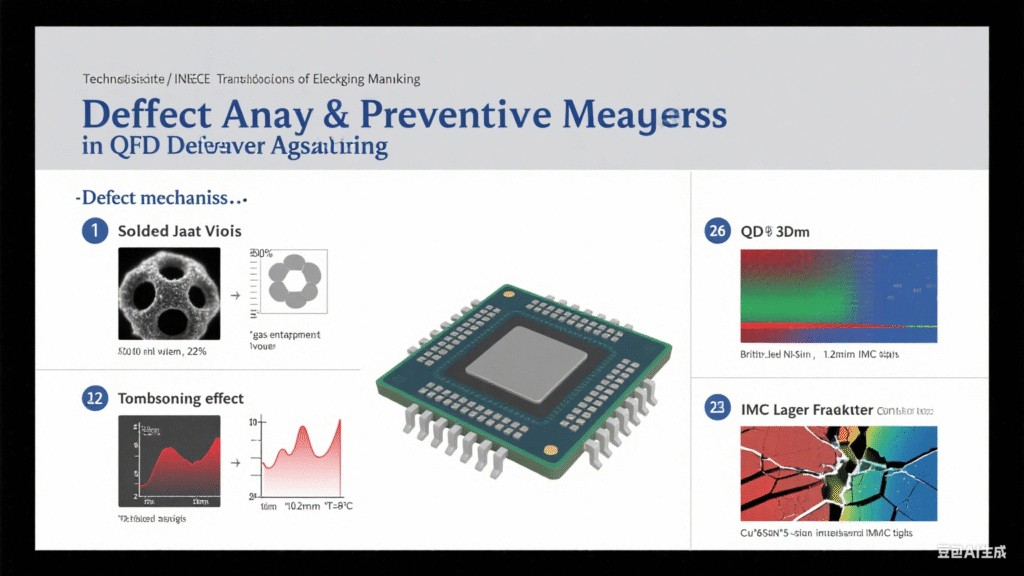

Assembly Process Defects and Mechanism Analysis

1) Fine-pitch signal pads prone to bridging

QFN pads are planar and nearly flush with the package bottom (0–0.05 mm in height). Together with PCB pads, they form a “surface-to-surface” solder joint. The large central thermal pad influences the solder joint height of the surrounding pads due to solder paste surface tension. Thus, the solder paste volume printed on the PCB thermal pad directly affects the solder joint quality.

For fine-pitch QFN packages (0.3 mm or 0.4 mm pitch), solder paste volume control is critical.

- Excessive paste: causes solder spreading, component floating, pad bridging, or even open circuits.

- Insufficient paste: leads to device collapse, signal pad solder joint bridging, or weak solder connections.

2) Large exposed thermal pad prone to voiding

QFN packages feature a large exposed thermal pad at the bottom, which makes void control difficult. Since the solder joints are “surface-to-surface” with very low standoff height, solvents in the solder paste are trapped in molten solder during reflow, forming voids upon cooling.

- If the total void area < 50% of the solder joint, thermal and electrical performance is not degraded, and reliability is unaffected.

- If a single void exceeds the via spacing, it significantly impacts high-speed and RF signal performance.

3) Insufficient solder wetting on side terminals

QFN packages can be separated by stamping or sawing. Saw-singulated QFNs may have either full-lead exposure or recessed-lead structures:

- Full-lead type: entire lead thickness is exposed on the package sidewall.

- Recessed-lead type: only the upper half of the lead is exposed due to half-etching.

Since QFN leads are plated before singulation, the cut edges remain unplated and expose bare copper. Over time, copper oxidizes during storage, reducing solderability. During reflow, this oxidation leads to poor solder wetting, insufficient side fillet formation, and lack of toe solder fill. For high-reliability applications such as military electronics, QFN side solder joints are required to achieve 100% solder wetting for stable electrical and mechanical performance.

Assembly Process Defect Prevention Measures

Based on the analysis, the main assembly defects of QFN devices include:

- Signal pad bridging

- Thermal pad voiding

- Insufficient side solder fillet height

These are influenced by PCB pad design, solder paste volume, flux activity, reflow profile, and standoff height. Effective prevention requires co-design of PCB layout and stencil.

1) Signal pad design

- PCB pads should be slightly larger than QFN terminals (width: 0.25–0.50 mm, length: 0.60–0.96 mm).

- Toe extension: 0.1–0.2 mm, heel extension: >0.05 mm.

- Minimum clearance between signal pads and central thermal pad: ≥0.2 mm to avoid bridging.

2) Thermal pad and via design

- PCB thermal pad should extend 0–0.15 mm beyond the exposed pad edge.

- Clearance between central pad and signal pads: ≥0.2 mm.

- Thermal vias: diameter 0.2–0.3 mm, 1 oz Cu plating, pitch 1.0–1.2 mm, with 40–60% coverage area.

- Via tenting (solder mask) is recommended to prevent solder wicking. Top-side solder mask gives smaller voids compared to bottom-side filling.

3) Signal pad stencil design

- Optimal solder joint height: 50–75 μm.

- Stencil aperture ratio: area ratio >0.66, aspect ratio >1.5.

- Aperture size = PCB pad size (1:1).

- For recessed-lead QFNs, aperture size should be slightly reduced.

- For fine-pitch QFNs (≤0.4 mm), stencil apertures should be reduced to minimize bridging.

4) Thermal pad stencil design

- Use multiple small apertures instead of one large opening.

- Aperture shape: circular or square, array pattern.

- Recommended solder paste coverage: 50–80% of pad area.

5) Stencil type and thickness

- Stainless steel stencils recommended; laser-cut and polished.

- Nano-coated stencils improve solder paste release and reduce voids.

- Tapered apertures ensure smooth paste release.

- Recommended stencil thickness: 0.12 mm for pitch ≤0.5 mm, 0.15 mm for larger pitch.

- Pre-tinning QFN leads and using nitrogen reflow can improve side solder wetting.

Conclusion

QFN packages, with their superior electrical and thermal performance, are widely used in modern electronics. However, their leadless design and large exposed thermal pad present significant challenges in PCB assembly. Common defects include bridging, voiding, and insufficient side fillet solder height. Proper PCB pad design, stencil optimization, solder paste control, and reflow environment management are essential to ensure high-reliability QFN assembly.